Chip » 芯片(一)——摩尔定律的瓶颈, 芯片行业

2024-04-10 :: 4680 Words摩尔定律的瓶颈

上世纪60年代,摩尔发现半导体晶体管制程发展的速度对于一个半导体厂商至关重要。

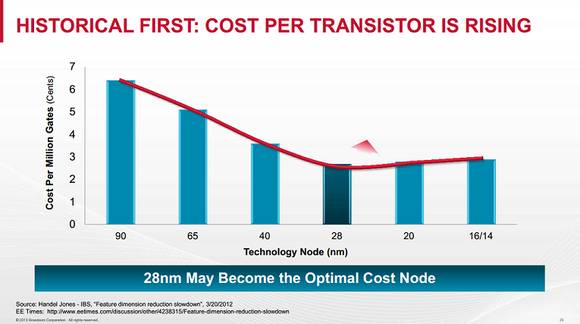

随着制程的进化,同样的芯片的制造成本会更低,因为单位面积晶体管数量提升导致相同的芯片所需要的面积缩小。所以制程发展速度如果过慢,则意味着芯片制作成本居高不下,导致利润无法扩大。

另一方面,如果孤注一掷把所有的资本都用来发展新制程,则风险太大,一旦研发失败公司就完蛋了。

摩尔发现当时市场上成功的半导体厂商的制程进化速度:集成电路上可以容纳的晶体管数目在大约每经过18个月到24个月便会增加一倍。于是他写了著名的论文告诉大家,这个发展速度是成本与风险之间一个良好的折中,半导体业以后发展可以按照这个速度来。(Moore’s Law)

芯片的成本包括NRE成本(Non-Recurring Engineering,指芯片设计和掩膜制作成本,对于一块芯片而言这些成本是一次性的)和制造成本(即每块芯片制造的成本)。

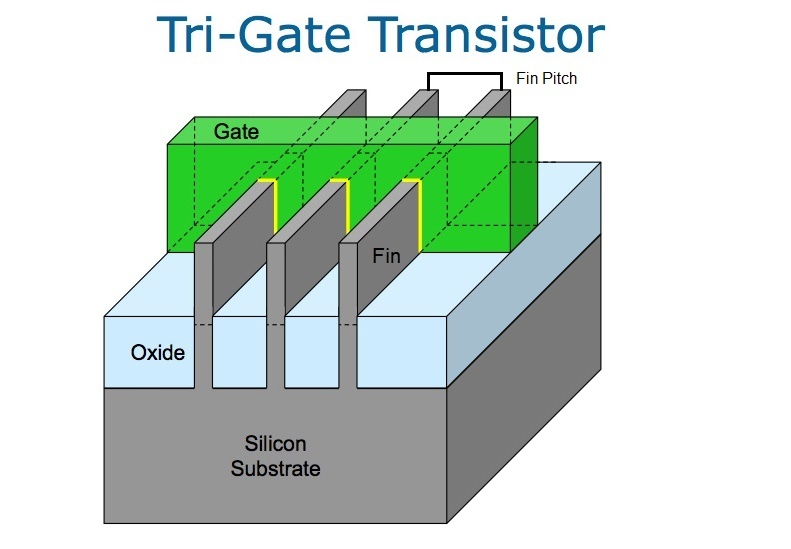

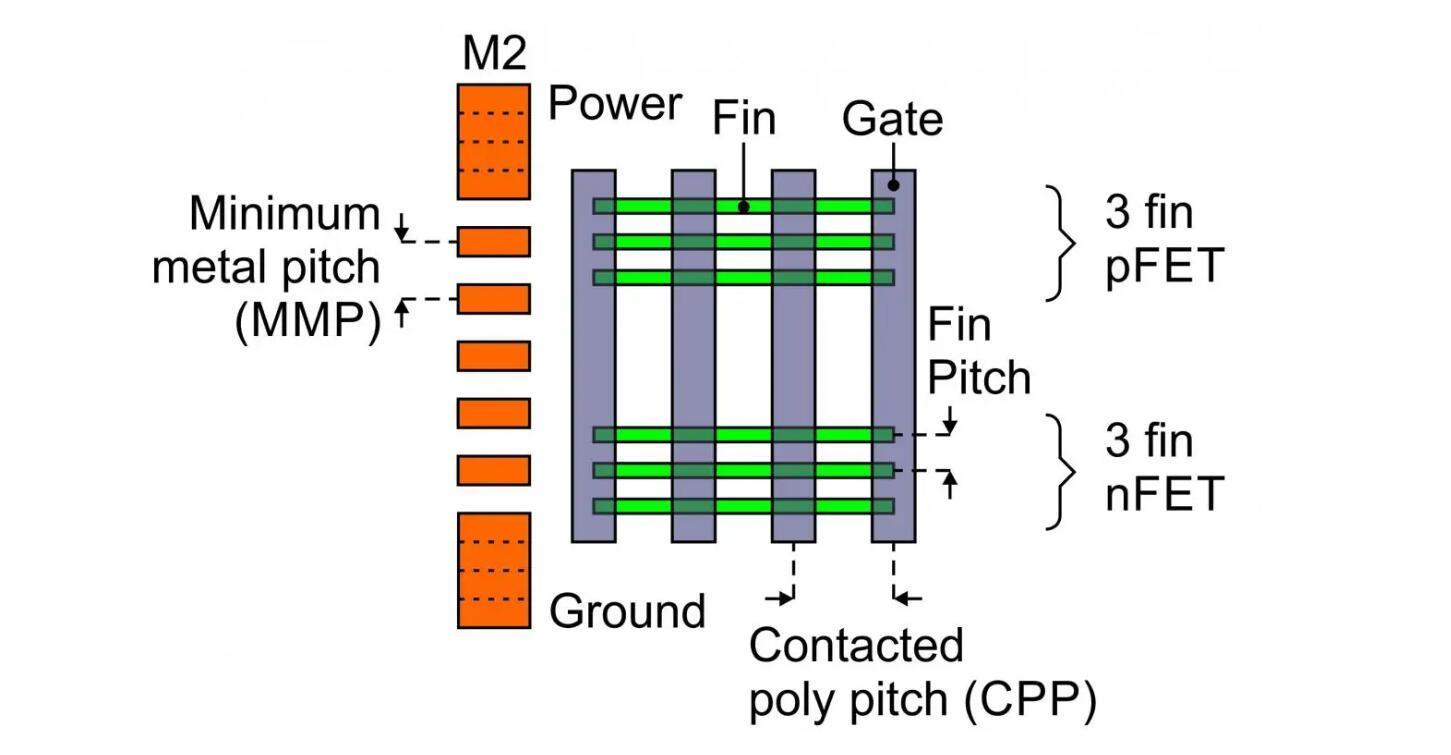

在先进工艺制程,由于工艺的复杂性,NRE成本非常高。例如FinFET工艺往往需要使用double patterning技术,而且金属层数可达15层之多,导致掩膜制作非常昂贵。另外,复杂工艺的设计规则也非常复杂,工程师需要许多时间去学习,这也增加了NRE成本。

对于由先进制程制造的芯片,每块芯片的毛利率较使用落后制程制造的芯片要高,但是高昂的NRE成本意味着由先进制程制作的芯片需要更多的销量才能实现真正盈利。这使得芯片设计和制造所需要的资本越来越高,而无力负担先进工艺制程的中小厂商则不得不继续使用较旧的工艺。这也部分地打破了摩尔定律“投资发展制程-芯片生产成本降低-用部分利润继续投资发展制程”的逻辑。

Andy gives, Bill takes away.

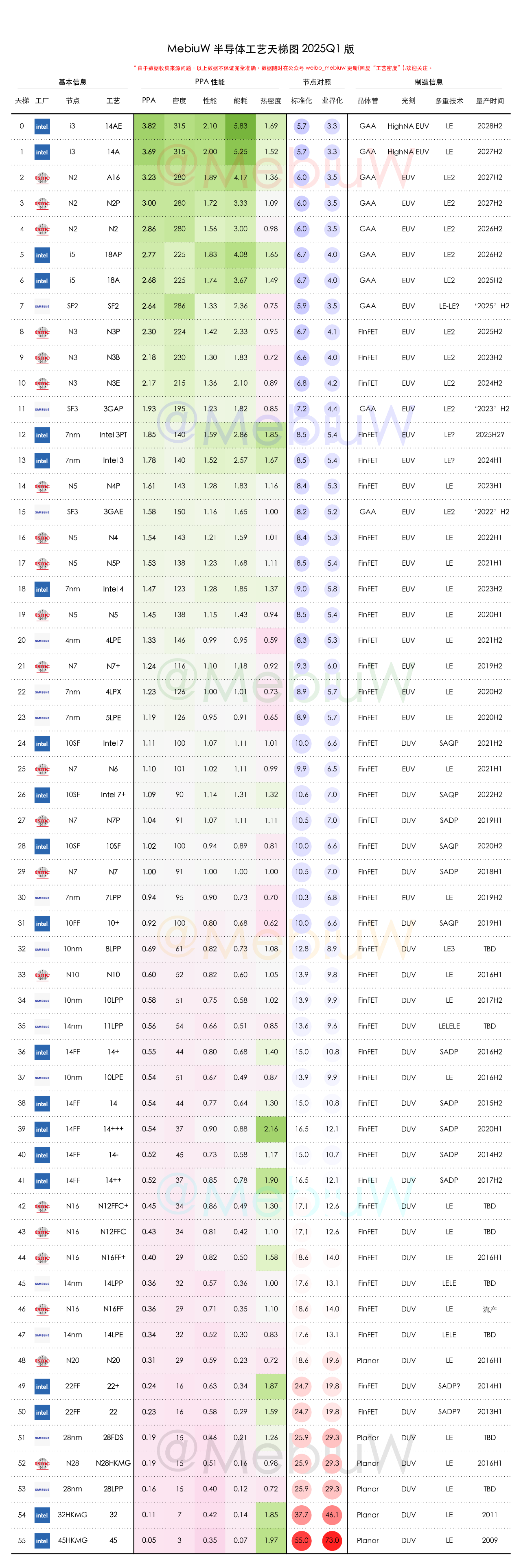

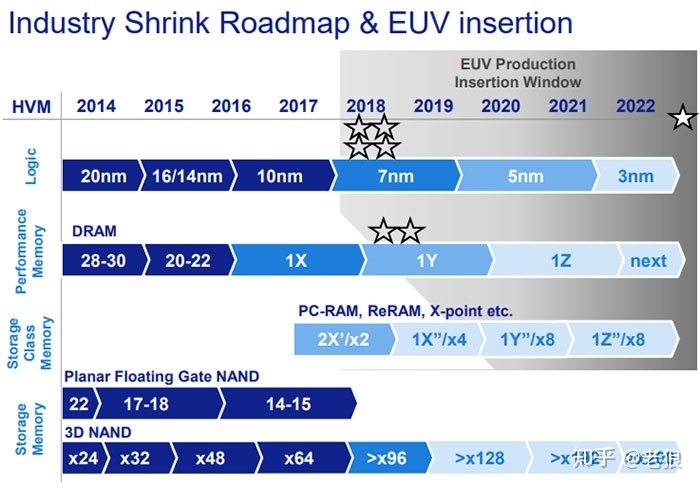

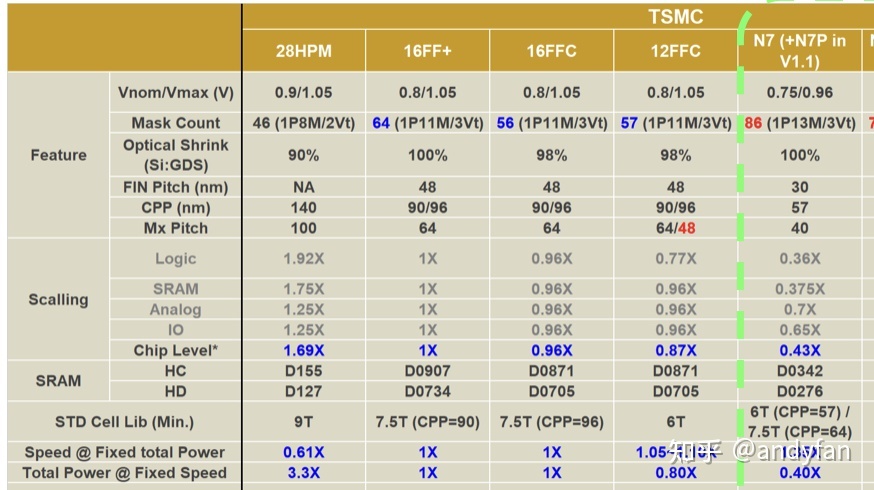

TSMC的命名规则里NxP相比Nx,密度一样,但是成本、良率和功耗都有改进。通常也是该制程的最终定型版本。

https://mp.weixin.qq.com/s/TmLSHVkeyqfU-9Jgir0czA

摩尔定律究竟死没死

对设计公司来说,28nm节点上的开发需要投入5310万美元,16nm需要1亿美元,而到了7nm,则需要将近3亿美元。在这之中,仅仅流片一项付出的成本,就从14nm的300万美元跃升至7nm的3000万美元。所以7nm就算降价,还是贵。

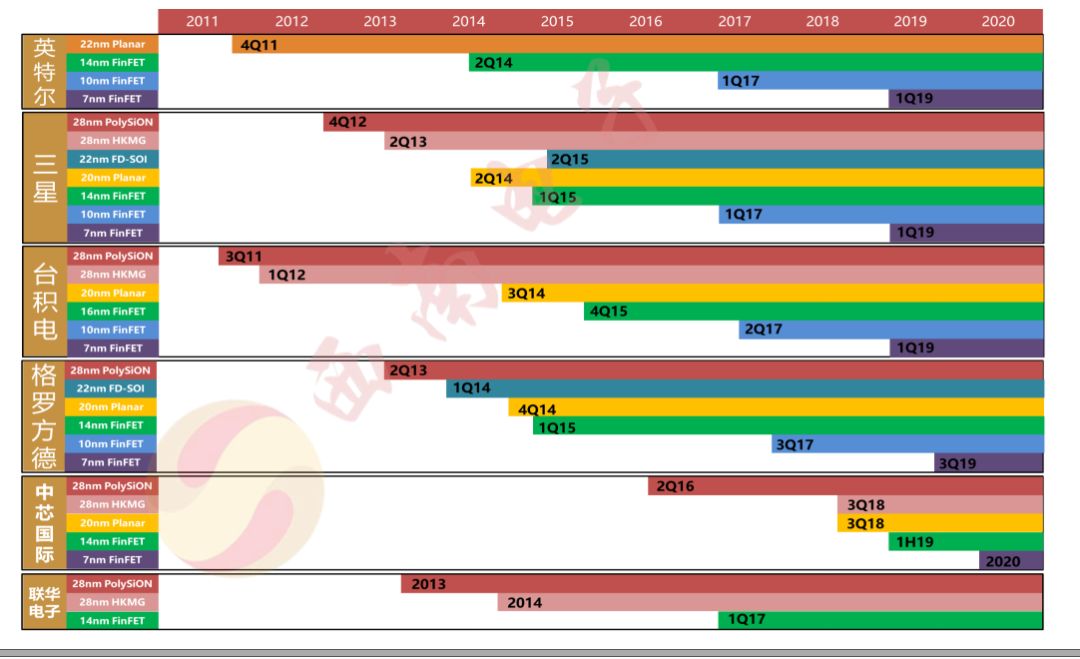

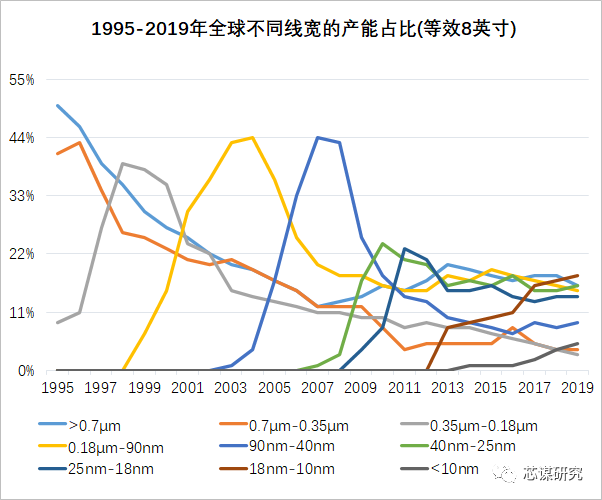

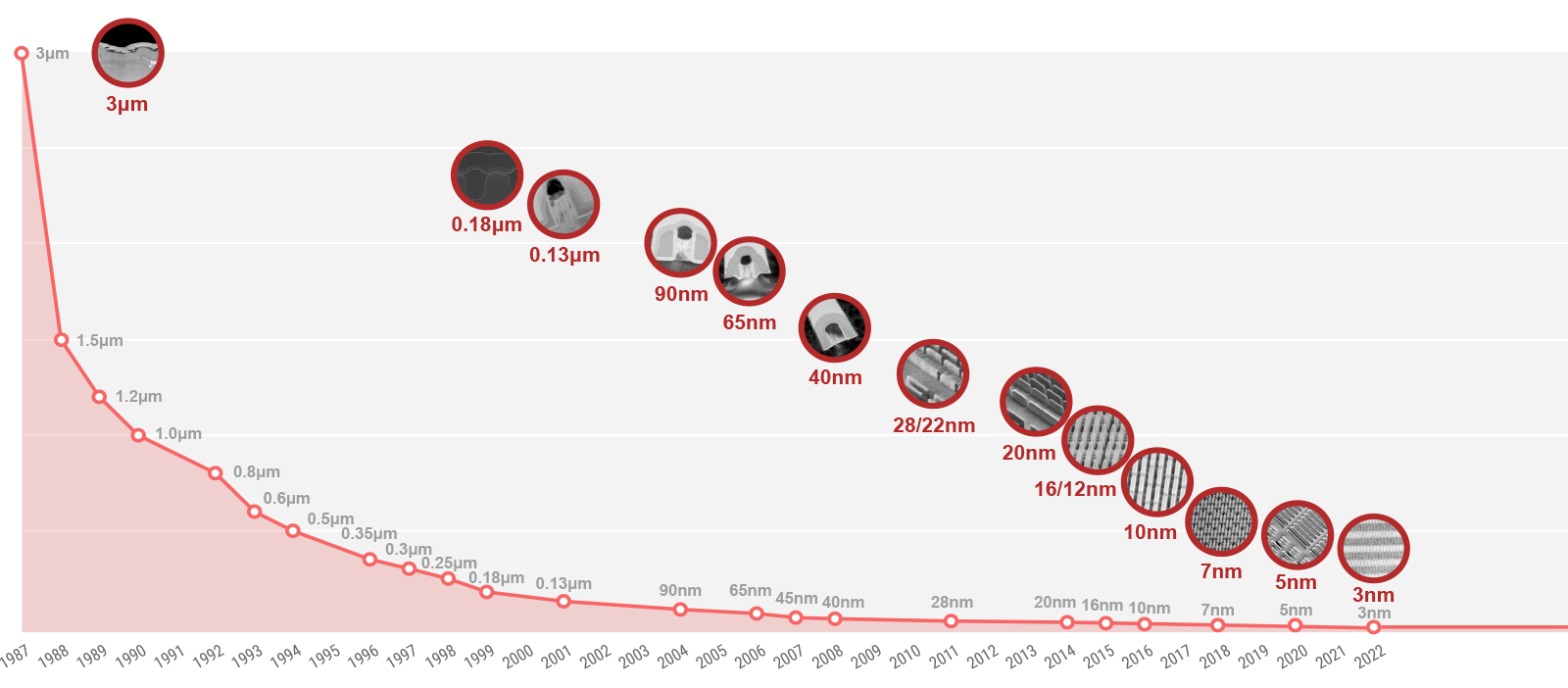

从上图可以看出:2008年以前,先进制程有一个明显的爬坡阶段,但是如今由于成本的影响,更像是百花齐放了。

针对成本问题,IRDS在2020提出了PPAC概念,即每2-3年P(性能)提升15%,P(功耗)减少30%,A(面积)减少30%,C(成本)晶圆成本增加少于30%。

从PPAC来看,密度的Moore’s Law已经变缓了,但功耗的Moore’s Law仍然可以延续。

芯片内部有多种单元,有高密度晶体管,也有低密度晶体管,也不是处处都有110 MTr/mm2这样的高密度,由于SRAM结构和对Vt和Isad的敏感特性,导致SRAM区域的面积就已经出现了停滞不前的现象。

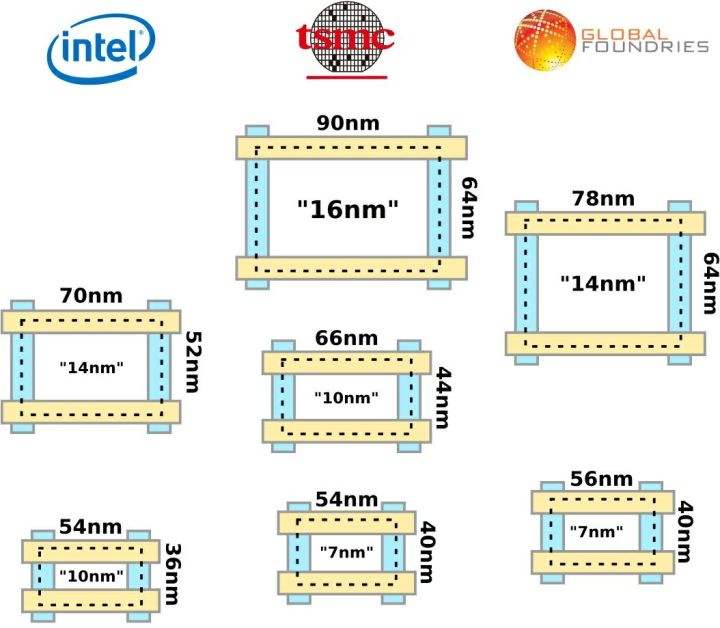

除了fin width(鳍的宽度)和gate length(栅极长度)这俩数据还相对接近我们所说的10nm/7nm这个工艺名称,其他各部分pitch/尺寸都没有达到或接近10nm/7nm的。

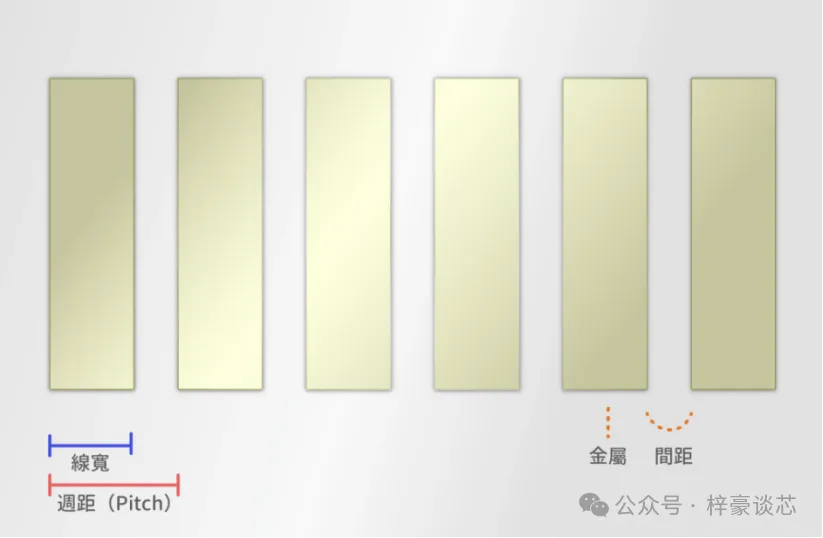

以前(在190nm以前),我们听到的这个工艺数字特指的就是gate length…,但在190nm以后工艺名称的数字增长,和实际gate length的缩减就已经不同步了。在7nm尤其是5nm以后,变得越来越没有关系…

90年代,0.35μm以前,工艺节点、半周距(Half pitch,即周距的一半)与栅极长度均一致,但在这之后,半周距、栅极长度与节点的对应关系出现分歧。

摩尔定律的节点推进时间从原本18个月到24个月,进入7nm以后则是延缓到30个月,2018年量产7nm,2020年量产5nm,2023量产3nm,2025量产2nm,大概为2~3年左右推进一代。以目前可知技术来看,1.4nm还能保持目前速度,1nm往后节点大概率拉长到40个月以上.

没有统一的标准自然会被企业拿来玩文字游戏模糊概念,三星在其14nm节点首开先河,台积电为了不落人后马上跟进,但保守的定义为16nm,只有自诩为“摩尔定律”坚定追随者的英特尔,当时还在死磕传统线宽的命名方式,直到2021年才全面修改节点命名,10nm改成Intel 7,原本的7nm改成Intel 4,并把后续节点细化成了Intel 3、Intel 20A、 Intel 18A。

1971年:10微米

1974年:6微米

1978年:3微米

1982年:1.5微米

1989年:1微米

1993年:0.8微米

1994年:0.6微米

1995年:0.35微米

1997年:0.25微米

1999年:0.18微米

2001年:0.13微米

2004年:90nm

2006年:65nm

2008年:45nm

2010年:32nm

2012年:22nm

2015年:14nm

2018年:7nm

2020年:5nm

2022年:3nm

2025年:2nm

| 制程 | 出局厂商 |

|---|---|

| 180nm | SilTerra X-FAB Dongbu |

| 130nm | HiTek ADI Atmel Rohm Sanyo Mitsubishi ON Hitachi |

| 90nm | Cypress SkyWater Sony Infineon Sharp Freescale |

| 65nm/45nm/40nm | Renesas Toshiba Fujitsu TI |

| 32nm/28nm | Panasonic STMicroelectronics HLMC |

| 22nm/20nm | IBM |

| 16nm/14nm | UMC SMIC GlobalFoundries |

10nm以下幸存者:Samsung TSMC Intel

https://www.sohu.com/a/483240732_121124379

回顾CPU制程工艺发展

Tick-Tock(工艺年-构架年)是Intel的芯片技术发展的战略模式,也被称为嘀嗒模式或者钟摆模式。

https://www.zhihu.com/question/290382241

为什么memory制程比CPU的制程低?

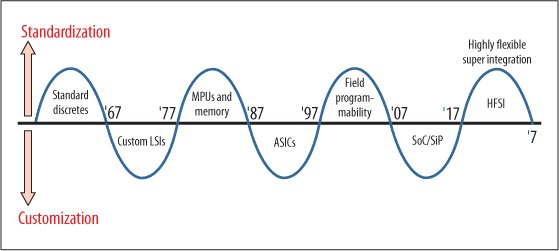

Makimoto’s Waves

Tsugio Makimoto(牧本次生),IEEE Robert N. Noyce Medal(2018)。曾任索尼CTO。半导体工业从NMOS到CMOS演进的先驱。

MOSFET device scaling principles,又称为Dennard缩放比例定律(Dennard scaling, 1974)表明,随着晶体管变得越来越小,它们的功率密度保持不变,因此功率的使用与面积成比例;电压和电流的规模与长度成比例。

Dennard scaling是Moore’s Law的物理基础,而后者仅仅是个行业规律而已。

https://mp.weixin.qq.com/s/7kRePPUk_Xat8-7PsAO5XQ

晶体管逐渐变小,Dennard定律比摩尔定律更值得关注,散热和功耗推动芯片专业化

PPA(Power-Performance-Area)

Robert H. Dennard,1932年生,Southern Methodist University本科(1954)+硕士(1956)+CMU博士(1958)。IBM研究员,DRAM发明者。美国工程院院士,IEEE Fellow。

https://www.yicai.com/news/100419064.html

科技创新里程碑:IBM科学家Robert H. Dennard与改变世界的芯片

最后两行就说的是固定功耗能达到的最大速度,和固定速度需要的功耗;面积的比较是在上面,不同macro微缩的比例是不一致的。

https://www.zhihu.com/question/512906953

22nm芯片能做到7nm一样的性能吗?

https://zhuanlan.zhihu.com/p/614318358

“双”浅谈14nm+14nm>7nm是否真的可行

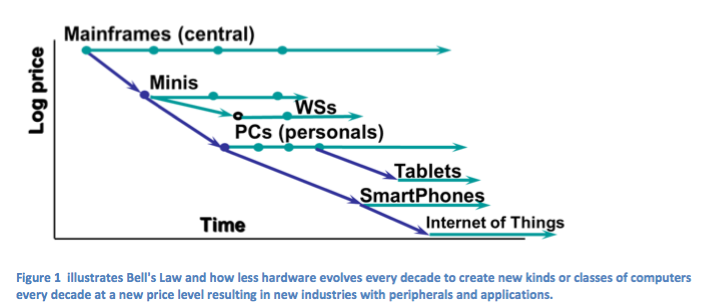

Bell’s law of computer classes(1972):计算机每10年产生新一代,其设备或用户数增加10倍。

C. Gordon Bell,1934年生,MIT本科(1956)+硕士(1957)。DEC公司的技术灵魂人物(1958~1983),DEC创始人Kenneth Olsen的学弟和创业团队成员。

https://www.zhihu.com/question/20809971

多核之后,CPU的发展方向是什么?

摩尔定律的黄金时代,靠着工艺进步,软件工程师可以近乎无感地快速享受到硬件性能的红利。随着单核性能提升放缓,软件工程师需要关注更多多核的编程细节,来释放硬件的性能红利。随着单芯片能放的核数也日趋瓶颈,DSA架构、封装技术的演化、甚至System-on-Wafer的技术都涌现出来,期望能够进一步压榨晶体管的性能,也相应地对软件栈提出了更高的要求。

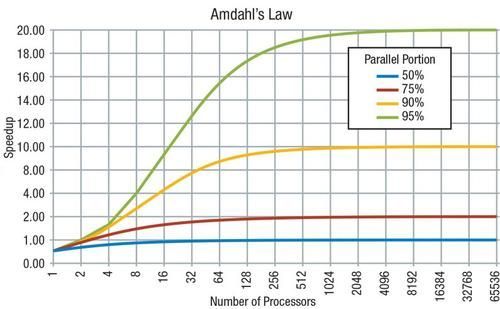

系统中对某一部件采用更快执行方式所能获得的系统性能改进程度,取决于这种执行方式被使用的频率,或所占总执行时间的比例。

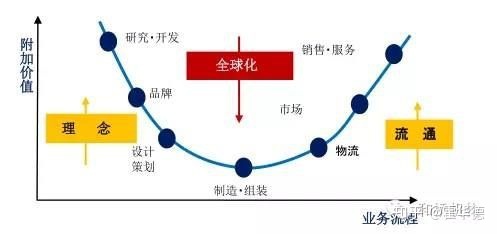

产业价值链最底层的生产制造领域,即微笑曲线的中间。很多学理工科的人都有这个幻觉,觉得自己做技术做的价值曲线最左端的研发,有着光明的前途。但实际上99%的(对口就业)理工科学生最后都去了生产制造。对于新加坡的芯片行业,其实真正的研发是0,技术全部都是依靠欧美转移。

什么算真正最左侧的研发。还是以芯片光刻胶为例,国外光刻胶阻抗可以做到\(10^{15}\),国内只能做到\(10^{10}\),阻抗越高纯度越高,这中间是十万倍的差距。

微软对Arm服务器的评价:

“我并不需要你帮我省电,而是希望你帮我把更多的电变成更多的钱”

TSMC的28nm工艺有多个版本:

- 28nm LP(Low Power)

- 28nm HPM(High Performance for Mobile)

- 28nm HPC(High Performance Computing)

- 28nm HPC+(High Performance Computing Plus)

芯片行业

IC行业的公司一般分为全流程的(IDM),著名公司如德州仪器,英特尔,三星,意法半导体,只做设计自己没有晶圆厂的(Fabless),比如英伟达,AMD,只负责制造的(Foundry),比如台积电。

IDM -> Fabless -> Designless

系统厂商负责产品定义、核心技术开发、Design Service负责系统厂商无力cover的其它芯片设计流程,Fab负责芯片生产,封测厂负责芯片测试。

SOC的难点在于SOC的架构设计和验证完备上,虽然不同意SOC设计是连连看的观点,但是SOC的能力关键确实不在设计上。

台湾三大科学园区为竹科(新竹科学工业园)、中科(中部科学工业园)、南科(南部科学工业园)。台积电研发主要在竹科、量产在中科及南科。

您的打赏,是对我的鼓励