Chip » 光刻

2024-09-17 :: 4211 Words光刻

概述

半导体光刻术起源于20世纪50年代中期,当时一位名叫杰伊·拉索普(Jay Lathrop)的物理学家将显微镜中的镜片倒置。

缩短波长的方法除了增加频率之外,其实还有更换介质(比如水),这就是浸润式微影。不同工作波长,液体也不同。需要考虑液体的吸收作用。

Rayleigh criterion(瑞利判据):

\[CD = K_1 \frac{\lambda}{NA}\]\(K_1\)是一个常数,取决于与芯片制造工艺有关的许多因素。按照ASML的说法,其物理极限值是0.25。\(\lambda\)则代表光刻机使用光源的波长;NA则是光学器件的数值孔径,描述了它们能够收集光的角度范围;CD代表线宽,即可实现的最小特征尺寸。

DUV是深紫外线(Deep Ultraviolet Lithography),EUV是极深紫外线(Extreme Ultraviolet Lithography)。

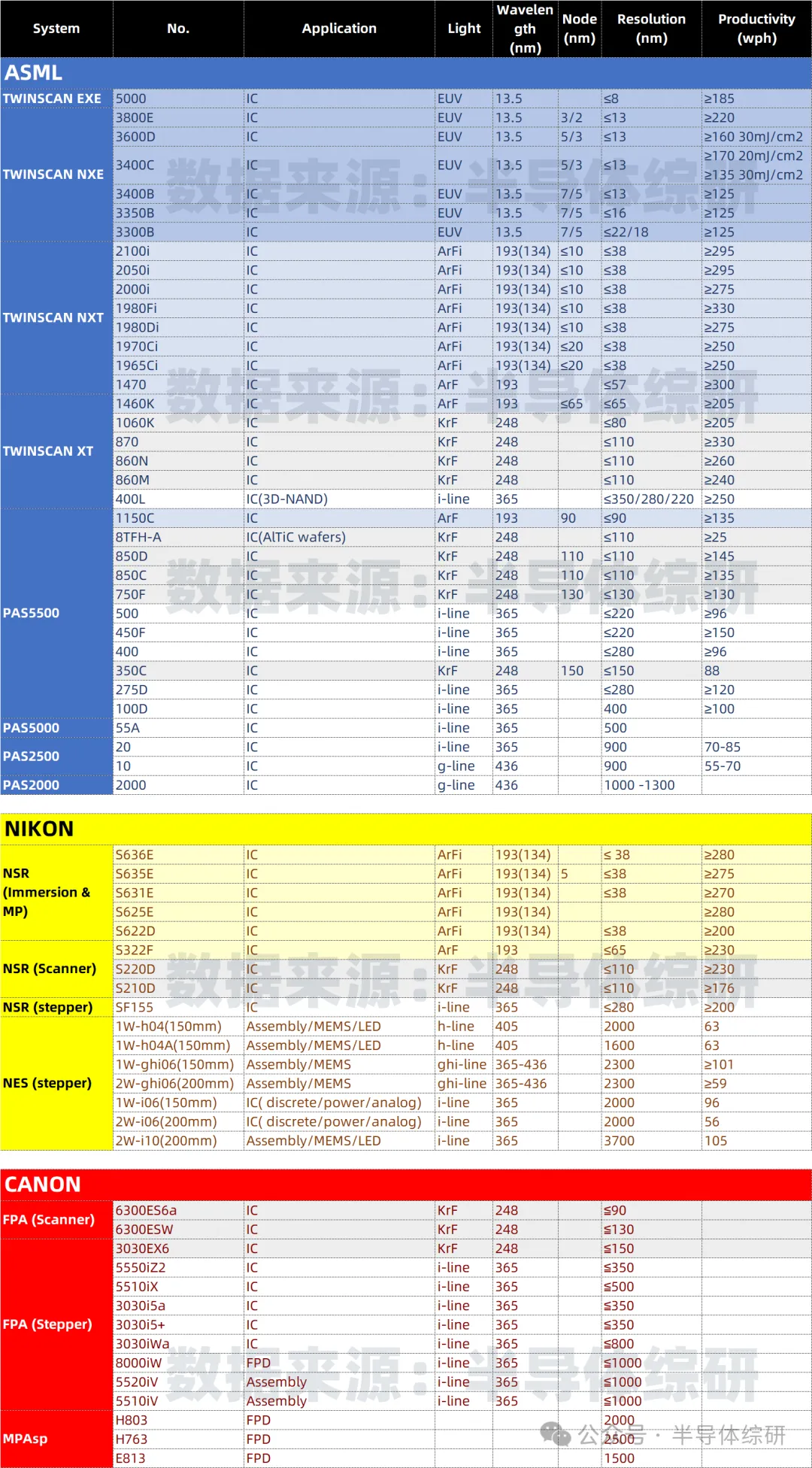

ASML光刻机分为四大等级:

A、EUV7nm及以下。

B、DUV湿法先进制程16-7nm。

C、DUV湿法成熟制程45-28nm。

D、DUV干法110-65nm。

https://www.zhihu.com/answer/2017184228710843701

光刻机相关参数图示

套刻精度

光刻机的套刻精度(Overlay Accuracy)是指在光刻过程中,不同光刻层之间对齐的精确度。在半导体制造中,芯片的制造涉及到多层材料的叠加,每一层都需要通过光刻过程来形成特定的图案。这些图案层需要非常精确地对齐,以便在后续的工艺步骤中能够正确地连接和构建电路。

光刻机的套刻精度(Overlay),它决定了芯片上下层的对准精度,进而决定了多重曝光的良率。

提高套刻精度的办法之一,就是拿到更高精度的设备,比如2100i DUV光刻机。目前能把多台套刻精度(MMO)做到无限接近单台套刻精度(DCO),全世界仅台积电一家。

台积电用MMO:2.5nm的1980ci光刻机+四重曝光良率超过80%,而大陆厂用MMO:1.5nm的2050i+四重曝光,经过2年的不断努力,良率接近50%。

多曝光对于套刻精度是苛刻的,每多一次砍一半。

单次曝光overlay的control window大约20%-25%的CD,所以65nm线宽的光刻机需要至少13nm的overlay。

如果要做双重曝光overlay必须降低一半也就是13nm/2=6.5nm,这就是目前这台国产光刻机无法做多曝的理论依据。

ASML表示,其TWINSCAN NXT:1980系列浸润式光刻系统的DCO值小于等于1.6nm,因此不受新规定的限制,可以继续出口。但是,对于更先进的TWINSCAN NXT:2000i及后续推出的系统,ASML需要申请出口许可证。

哪怕搬到外太空用恒星做光源,光刻也要对准、量测、扫描。就在5月底,ASML还在国内中标了4台248nm的KrF,EUV造不了、ArFi造不了、ArF造不了都不提了,然而现状是赢学家一顿吹下来,波长248nm的KrF都还在买ASML,难道是看ASML可怜赏他一口饭吃吗?

提高分辨率还可以使用双光束成像(2-beam Imaging)的方法,分别有偏轴式曝光(OAI)及移相光罩PSM)两种。

偏轴式曝光是调整光源入射角度,让光线斜射进入光罩。透过角度的调整,可以很巧妙地让这两道光相互干涉来成像,使分辨率增加并增加景深。

移相光罩则是在光罩上动些手脚,让穿过相邻透光区的光,有180度的相位差。这两种做法都可以让k1减少一半,不过这两种方法都是用2-beam Imaging的概念,不能叠加使用。

要再进一步降低k1,最终的杀手剪!就是用两个以上的光罩,也就是大家耳熟能详的多重曝光(Multi-patterning) 。

多重曝光的手艺是当年intel投入重金搞的,有LELE,LFLE和SADP/SAQP三种。

- LELE,Litho-Etch-Litho-Etch,光刻-刻蚀-光刻-刻蚀。把原来一层光刻图形,划分到两个或多个掩膜上,搞了一次图像叠加。这个好想象。

- LFLE,Ltiho-Freeze-Ltiho-Etch,光刻-固化-光刻-刻蚀。和LELE本质差不多,省一道刻蚀工序,降低成本。

- SADP,Self Aligned Double Patterning,自对准双重图形化以及SAQP四重曝光技术。

结果突然EUV来了,Intel大呼上当。我在练射箭手艺,你给台积电造了一把冲锋枪。

多曝搞先进制程没有经济价值,甚至于对于当前的中国,连工艺研发和产业价值都有限。

N6这类初代EUVL制程本身所需掩膜就更少,外加EUV这么多年成本平摊和良率持续爬升、停掉SAQP Gate的ArFi产能释放,良率也因为process和steps的简化而提高,致使其性价比反超了ArFi的末代工艺。这就是局外人所无法理解的事情:虽然用了更昂贵的设备,但是由于综合产能和利用率的上升,单位成本反而降低了。

光源

目前全世界能生产光刻机的DUV光源只有美国Cymer跟日本Gigiphoton两家,美国Cymer是ASML的子公司并提共ASML DUV以及EUV光源系统,日本Gigiphoton是从小松独立出来的并向日本两大光刻机Nikon、Canon提供光源。

光源系统的核心部件”电源模块”02专项是由中科院安徽光机所方教授带领的团队承担攻关任务。目前性能为20W 4KHz。

小松在2001年就发表了安徽光机所同性能的光源,Cymer是在更早的2000年发表的,也就是说我们千辛万苦刚刚突破的光源技术是国外20多年前的水平。

ASML跟Nikon的光源系统在20年前的ArF dry光刻机中就达到40W 4KHz,而比dry更难的ArFi最新型号2050i更是达到120W 6KHz,每小时300片Wafer+的产能。

对于去年就开始传的SSA800/10W的28nm光刻机,我们可以发现他的光源功率只能达到10W。

其实把这几年国产光源系统的表现对应2000年前后Cymer跟Gigiphoton光源的提升,我们能发现国产光源并没有出现后发优势,Cymer跟Gigiphoton一直是每1.5~2年提升一个台阶,但国产光刻机以ArF dry来说2019年我们已经掌握20W的光源制造能力,但2023年刚出货给燕东微的SSA600还是20W 4KHz。

在EUV波长区域,并没有天然的材料与机制可以产生激光,现行的13.5nm EUV是以二氧化碳激光照射掉落的锡液滴所激发的次级光源。

由于EUV光的产生过程复杂,光的频率集中的程度远不如使用激光源的DUV,亮度也远远不如DUV。亮度不足,曝光时间就需要较长,这就影响了光刻机产出效率(WPH)。

EUV光刻机功率达到了100万瓦,是上一代的10倍左右,每天耗电3万度。

镜头

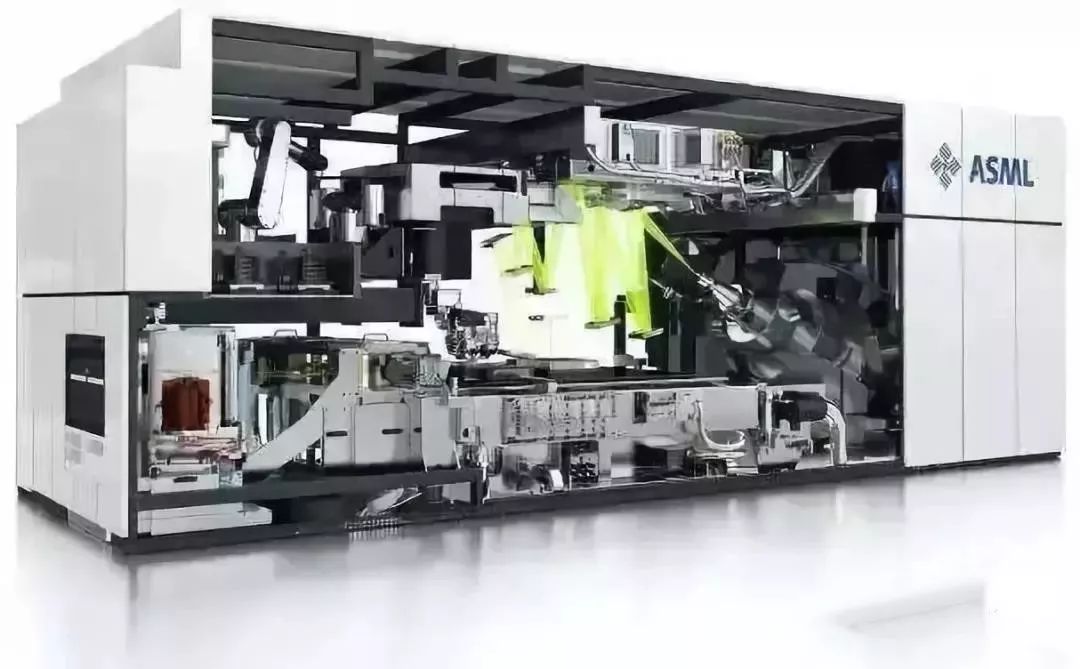

绝大多数人不知道的是,目前ASML光刻机里的光学模组(透镜组)也是蔡司提供的。而EUV光刻机的光学模组更是只有蔡司能够加工。

因为EUV光刻机使用13.5nm波长的光线,这种光线波长太短,短到不能用透镜来控制光线传播。因为透镜会对短波长的光线造成衰减,所以EUV光刻机只能通过反射的方式来形成光路。

要控制这种光线,需要几十层钼和硅层层叠叠摞起来,还要在镜片上镀膜才能完成,每一层膜都只有纳米级别的厚度,每层误差不能超过0.01纳米。

这样的镜面究竟有多平整?要求是起伏度要低于在地球表面大小的平面上放一根头发丝。

而目前拥有这样加工技术的公司只有蔡司。

奥林巴斯的电子和光学显微镜都不如徕卡,徕卡造了德国潜艇的潜望镜。

NIL

目前实现商业量产完成度最高的先进制程光刻机,其一是DUV/EUV光刻机,其二是NIL(Nanoimprint Lithography)光刻机。

DUV/EUV光刻机,主要涉及的企业是荷兰ASML和日本尼康。

1995年,华裔科学家周郁(Stephen Chou)教授首次提出纳米压印概念。

NIL光刻的相关企业:

Nanonex,就是周郁大佬参与的公司,总部在新泽西普林斯顿。

佳能,虽然是日本公司,但是佳能NIL光刻机大部分技术来自收购的Molecular Imprints,这家公司位于德克萨斯,至今佳能NIL光刻机的研发中心也还在德克萨斯奥斯汀。

HP,这个更是不用多说,几乎人人都知道HP是美国企业。

目前佳能推出的奈米压印机每小时产量就只有100片上下,100的WPH这比EUV的Alpha机器都还要低更别说量产机型,以现有技术来看掩模板可以使用的次数在几千次的数量级,因此我们清楚经过2-3天掩模板就得更换,所以在纳米压印技术中掩模板的成本将非常高。

EUV和DUV确实不是唯一的图形化技术。各路大神们经常提及的还有两种: 纳米压印和电子束曝光。

纳米压印的图形化良率太低。现如今一个芯片上有百亿个晶体管,纳米压印无法保证每个都正常。所以纳米压印只能用在容错率比较高的存储领域。没有任何一家的先进逻辑芯片是用纳米压印做的。

电子束曝光的分辨率可以高于EUV,这个是没错的。但是问题在于曝光的效率太低。和EUV先比,一个是请人抄书,一个是印刷厂印刷书。电子束写一个12寸片,是按天计时的,而EUV是按分钟计的。差了几万倍。所以电子束曝光一般只用于科研和加工光刻板。即使考虑很多个电子束的头同时写,也有本质上的问题:电子之间相互排斥,很多个一起写的话,每个头都写不准。

我们还是别老想着弯道超车了,毕竟有弯道的时候拐弯才能超车。

大家都走直道的时候你拐弯,那不会超车,只会翻车。

电子束光刻技术的优势是分辨率高(可以达到10nm以内,优于EUV光刻机),性能稳定,更为关键的是无需昂贵的掩膜板,综合成本非常低(单台设备约1000万美元)。这也使得该技术曾一度被认为是能够与EUV光刻机竞争的技术路线。

但是由于其速度太慢,效率低下,因此没有获得大客户的采用。2015年时,Mapper推出的Matrix 1.1版本设备(FLX-1200)使用1326束光,每小时只能生产1片基于28nm制程的晶圆。

https://zhuanlan.zhihu.com/p/12442508586

ASML收购Mapper的背后故事:中美俄荷四方暗斗

您的打赏,是对我的鼓励