Chip » CPU(一)——3D芯片, 片上网络, 总线, 封装

2019-04-08 :: 5400 WordsCPU

3D芯片

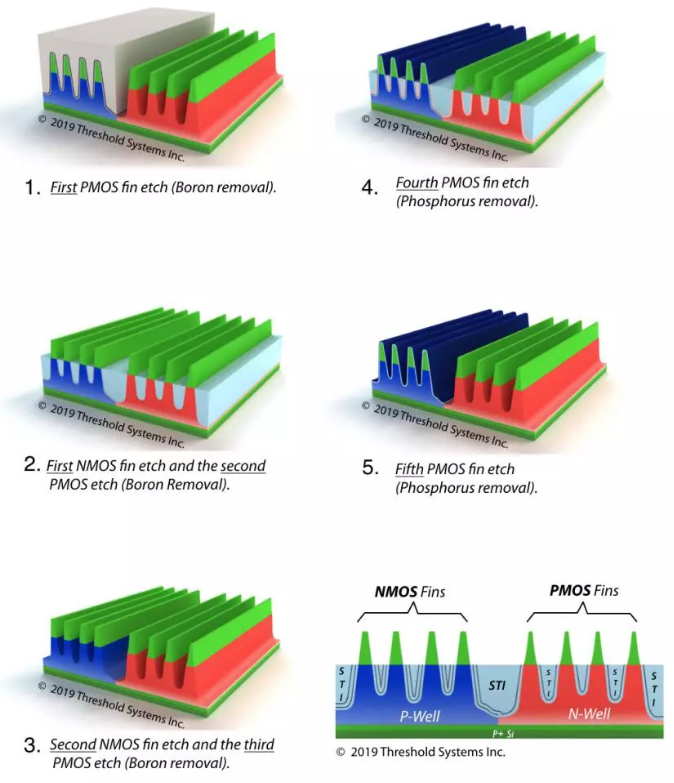

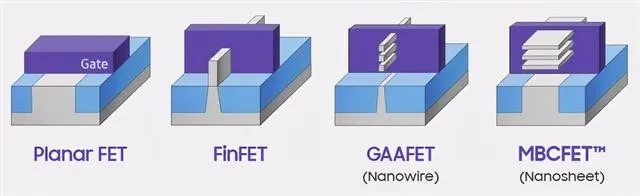

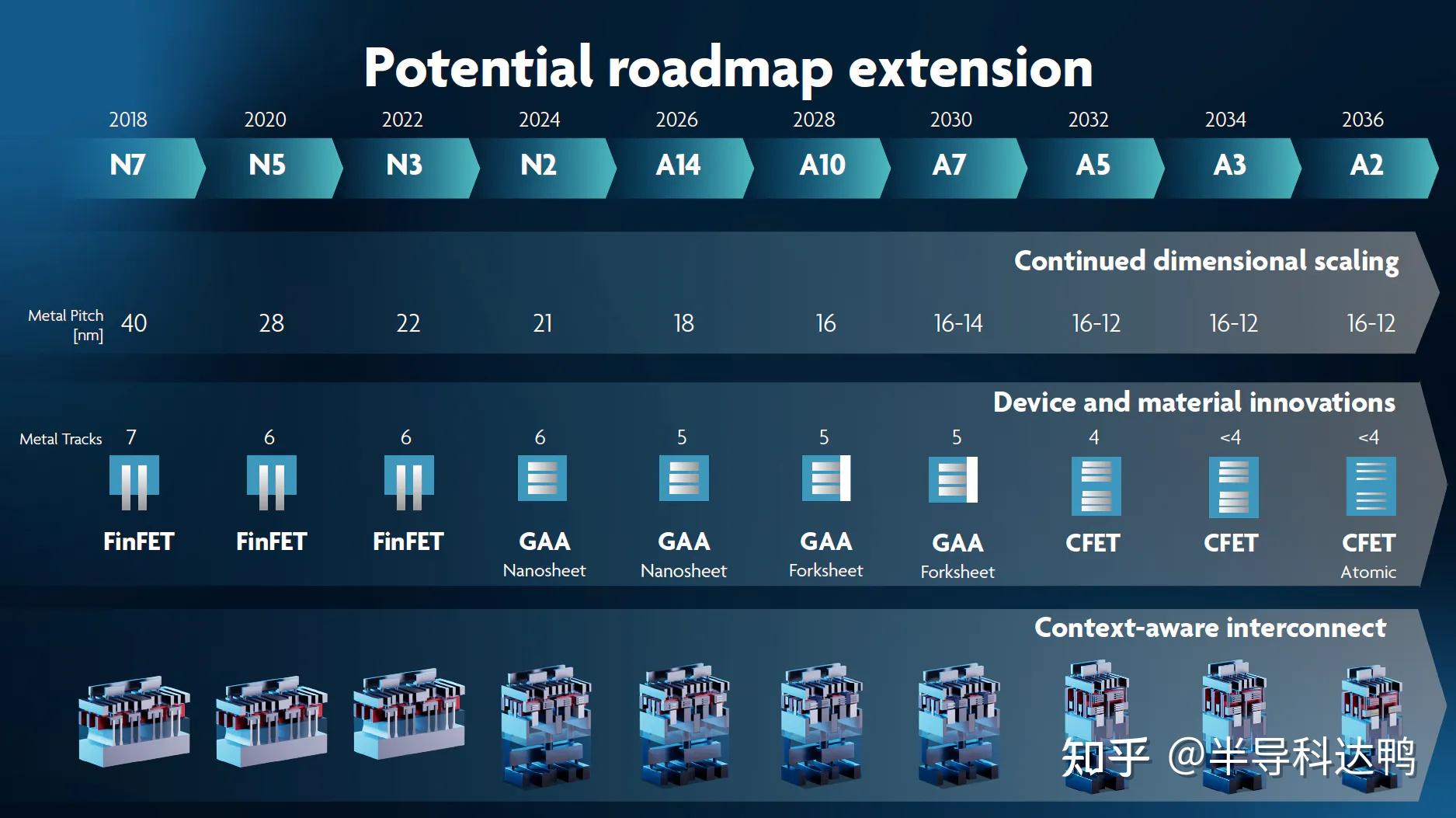

随着半导体工艺日益接近物理极限,2D芯片已经不能满足进化的需要,芯片的设计也迈向了立体发展的阶段。目前主流的3D芯片技术包括FinFET(1999)与FD-SOI(2000),他们都是胡正明团队的作品。

胡正明,1947年生。台湾大学本科(1968)+UCB硕博(1970,1973)。台积电首席科学家,MIT教授。美国工程院院士,中科院外籍院士。

单靠结构的改变,差别不大的线宽(20nm~16nm)却能推进至少6个世代,这也是为什么线宽早不像平面结构时的每两年缩小一倍,但是单位晶体管数量却能一直跟住摩尔定律的重要原因。

参考:

http://www.sohu.com/a/108777952_467791

多少年了,终于明白了FinFET与FD-SOI制程

https://mp.weixin.qq.com/s/NJBx8ndkBBedC81f3-DKOA

5nm以后的晶体管选择

https://mp.weixin.qq.com/s/YDFtuUlPtAYnJRYDuctOuA

胡正明获IEEE最高荣誉,一己之力续命摩尔定律数十年

https://zhuanlan.zhihu.com/p/260425739

FinFET的继任者:详解GAA晶体管

https://www.zhihu.com/answer/3389837693

现在ssd都可以用堆叠技术了,为什么CPU不能多堆几层呢,这样性能不就提升了吗?

https://www.zhihu.com/answer/3284871191

FinFET详解

nanosheet所需的highly-selective etch比EUVL推出还要晚,连ASML的EUVL都被纳入出口管制,就更别提LRCX和TEL的selective etch了,买不到设备怎么做nanosheet?

理论上什么节点都可以用GAA,但是成熟制程用传统平面工艺快速又高效,所以也不会有人犯傻将之用于低制程。

GAA用于7nm成本很高,良率会更低,但对于被限制的我国来说,这是必然的技术发展路线。

https://www.zhihu.com/question/620014852

DUV光刻机可以做GAA吗?

https://zhuanlan.zhihu.com/p/677687329

半导体制造红宝书 - 关键词100个(合集)

片上网络

片上网络network-on-chip(NoC)是片上系统system-on-chip(SoC)的一种新的通信方法。它是多核技术的主要组成部分。NoC方法带来了一种全新的片上通信方法,显著优于传统总线式系统(bus)的性能。

https://zhuanlan.zhihu.com/p/63683111

详说片上网络之一:片上多核系统与片上网络的发展

https://zhuanlan.zhihu.com/p/65501500

详说片上网络之二:片上多核系统的互联需求

https://zhuanlan.zhihu.com/p/68393867

详说片上网络之三:片上互联的需求与片上网络的研究意义

https://zhuanlan.zhihu.com/p/69012724

详说片上网络之四:片上网络研究的难与易

https://zhuanlan.zhihu.com/p/71775965

详说片上网络之五:网络分层模型在片上网络上的实现(上)

https://zhuanlan.zhihu.com/p/78672250

详说片上网络之六:网络分层模型在片上网络上的实现(下)

https://mp.weixin.qq.com/s/AW08yhPzBZqfys8CbOjrYg

详说片上网路(NoC)技术

https://www.zhihu.com/question/31049944

片上网络NoC为何还没有得到实际应用?

https://www.zhihu.com/question/521098765

用算力强大的SOC来控制汽车是不是能够大幅减少MCU的使用数量?

南北桥

北桥芯片则是整个主板的数据交换中枢,整合有内存控制器以及AGP/PCI-E控制器等重要的控制功能,CPU、GPU与内存之间的数据交换都要通过北桥芯片进行;

南桥芯片则用于扩展外围I/O接口,例如SATA和USB接口等。

总线

ISA -> PCI -> AGP -> PCI-E

CXL全称是Compute Express Link。是一种开放工业标准用于高带宽低延迟的设备互联。它可以用来连接CPU和Accelerator, Memory Buffer以及Smart NIC等类型的设备。用于AI Machine Learning,高性能计算等场景。

CXL基于PCIe 5.0的物理层。我们已经有了PCIe,为什么还要再搞出一个新的CXL呢?其实主要是因为PCIe不支持cache的一致性。

NIC:Network Interface Card

和NV Switch类似,PCIe也有PCIe Switch。价格同样不菲。

https://zhuanlan.zhihu.com/p/651836498

这颗博通芯片,涨到14万

PCIE插上之后,初始通信速率都是PCIE 1.0的,完成握手后,会协商跳入更高速率继续握手。

PCIe分为控制器(controller)和PHY两部分,控制器是数字电路,PHY包含PCS和PMA两部分,PMA是模拟电路。

从linux上pcie驱动代码上看,博通、高通、海思等公司都是采用的synopsys的pcie控制器。但这些大厂现在有没有自研的pcie ip我就不清楚了。。。

https://www.zhihu.com/question/618468070

pcie4.0的设备插在3.0的设备上可行吗,如果反过来又会怎样?

https://www.sohu.com/a/193807422_588758

PCI,AGP,PCI-E接口啥区别?

https://zhuanlan.zhihu.com/p/383878879

CXL简介

https://zhuanlan.zhihu.com/p/391094717

详解HBA、NIC与CNA的区别

https://zhuanlan.zhihu.com/p/646829255

PCIe体系结构

https://zhuanlan.zhihu.com/p/646920500

一些PCIE知识整理——带宽计算

https://mp.weixin.qq.com/s/QyPIXvwJ1yux_XxmeNI3hw

PCIe发展历程及常见插槽速度对比

https://www.zhihu.com/question/550129239

PCIe传输和DMA传输有什么区别吗?

历史

NetBurst可以说是Intel历史上最大的战略错误。

https://www.zhihu.com/answer/137624368

历史上有哪些“大力出悲剧”的产品?

https://mp.weixin.qq.com/s/-2kGkJzjay2WJzIpMs2Adw

IEEE盘点27款震撼世界的芯片

https://mp.weixin.qq.com/s/KhY-PPdvZ26Uy8xEgi70DA

纪念晶体管诞生71周年——改变世界30款芯片大阅兵!

http://m.uczzd.cn/webview/news?aid=15020380163392206798

你所不知道的经典科技发展史: 以前CPU是如何设计出来的

https://mp.weixin.qq.com/s/Lnolh9y0rf86wOGa-F1xmw

计算机的诞生史

https://mp.weixin.qq.com/s/f_rk-NPKNzYpbHOr5bgluw

一文了解半导体的过去、现在和未来

https://mp.weixin.qq.com/s/A6tc00Azj9AM-FApt5CkTQ

AMD YES!背后不为人知的故事

https://mp.weixin.qq.com/s/EfjhstpXsl6sG9q_-qQjXQ

世界半导体集成电路发展史

https://mp.weixin.qq.com/s/pSKQ3lRYV13qU_5DaOw2HQ

晶体管发展历程回顾

AVX

MMX直接使用了80bit的FPU寄存器中的64bit,对CPU整个流水线几乎没有影响;SSE的128bit相比80bit增加了48bit宽度还算可以接受。AVX的256bit,整个CPU的数据通道比80bit增加了三倍多,需要消耗三倍的晶体管,功率也增加了三倍。因此在严格限定功耗的场景如笔记本或者服务器中,CPU运行AVX应用时需要降低频率从而降低功耗。

为了适应DL领域的应用,AVX还添加了一个VNNI的扩展指令集(Vector Neural Network Instructions)。

参考:

https://www.zhihu.com/question/406517759

如何看待Linus Torvalds对AVX512的评价?

https://zhuanlan.zhihu.com/p/449878214

向量化引擎初探(一)

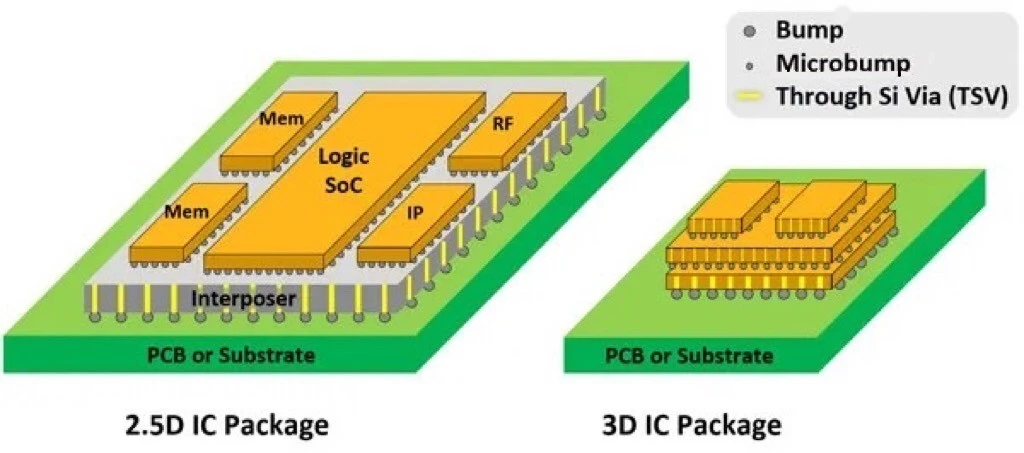

封装

BGA & QFP

BGA封装,就是那种引脚都在芯片背面的封装。QFP封装,即四侧引脚扁平封装。同样面积情况下,显然占据一个面的引脚数,要超过仅占据四个边的引脚数。

先进封装

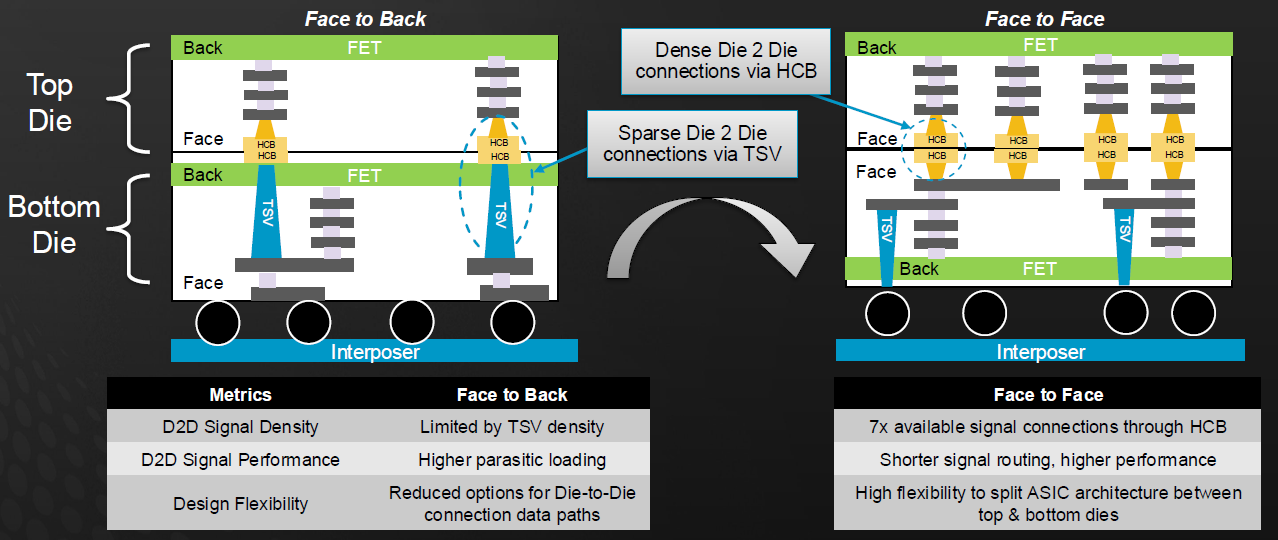

F2F的好处在于两个Die之间的高速互连无需通过TSV。

盛合是华为合作体系的厂商,完成华为昇腾和鲲鹏芯片的先进封装;通富微曾经也是长电/中芯的合作工厂,但如今是华为主导。两家都从事Chiplet封装,兼顾包括前道interposer的生产。

CoWoS(Chip-on-Wafer-on-Substrate)

TSV(Through Silicon Via)

CoWoS良率虽然要达到85甚至95%并不难,但这个良率数字跟前段那种50%70%的良率,意义上完全不同,后段CoWoS良率差1%都严重影响成本,因为前段处理的晶圆不值钱,但interposer上的GPU&CPU die还有大量的HBM却很值钱。

TSMC目前良率在99%以上,国内的盛H也就80%+的良率。

https://xueqiu.com/8992033978/256442528

一文看懂TSV技术

https://zhuanlan.zhihu.com/p/586478535

台积电芯片封装技术-CoWoS

https://mp.weixin.qq.com/s/FVcmCvimpoGCtCtm4RDtUg

浅谈先进封装技术

https://www.zhihu.com/question/652833460

中国可以自主实现CoWoS封装吗?国产CoWoS先进封装工艺发展到哪一步了?

https://zhuanlan.zhihu.com/p/699977071

CoWoS先进封装门槛到底是什么? 为何只有台积电独领风骚?

参考

https://mp.weixin.qq.com/s/vGONCRzvFGVo6giUFq0uag

芯片封装类型总结

https://mp.weixin.qq.com/s/RtSmbwguM7dbsXkWqAPuCQ

英特尔3D封装技术深度解读

https://zhuanlan.zhihu.com/p/54685671

PCB板上的黑色的物体是什么?

https://mp.weixin.qq.com/s/MQHZ-yLhZRIfOL9kN4XFKw

一文看懂3D封装技术及发展趋势

https://mp.weixin.qq.com/s/WBab6k4mIkZNzpvbgSbpVQ

一文看懂SiP封装技术

https://mp.weixin.qq.com/s/S-YGgvE6ey2t9_YmVmKOFg

一份难得的MOS管封装分析报告

https://mp.weixin.qq.com/s/MXuN1ccza508TMkcYVadvA

芯片封装简史

Cache

Cache本质上是一块小而快的存储设备和另一块大而慢的存储设备之间的协作关系。

Cache分为硬件Cache和软件Cache两种,这里只讨论前者。后者参见《数据库(二)》。

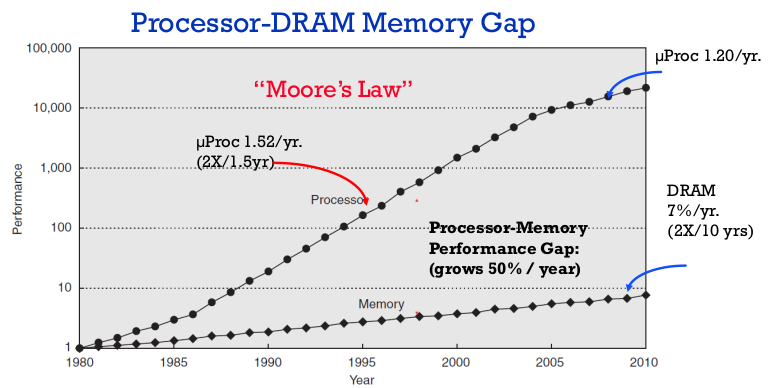

上图展示了CPU和DRAM之间的速度增长的差异,这个差异通常被称为Memory Gap。1980年代以前的计算机是没有Cache的,但是随着Memory Gap的增大,Cache的级数也不断增多,目前3级片上Cache+1级片外Cache已经是标配了。

必须指出的是,和CPU的速度受限于技术进步不同,RAM的问题主要是性能和价格的折衷。Cache实际上也是一种RAM,最好的L0 Cache和CPU的速度相当,只是价格太高而已。

类似这样的还有PCB的线宽。微米级的线宽技术上完全可行,毕竟芯片都已经是纳米级的线宽了,主要还是价格的问题。

您的打赏,是对我的鼓励