Chip » CPU(二)——Cache, Jim Keller, 内存一致性, RISC-V

2020-07-24 :: 5314 WordsCPU

Cache(续)

在一个多处理器系统中,Cache们和内存池可能对同一份数据有多份副本,如何保证这些副本的一致性(Coherency)是个必须严肃对待的问题。

多核CPU多级缓存的一致性,一般由相关的一致性总线协议保证。这些协议包括:MSI、MESI和MOESI。

https://mp.weixin.qq.com/s/570O2BloWjy3q0_m_mfiZg

CPU缓存一致性协议

https://zhuanlan.zhihu.com/p/63494668

显存为什么不能当内存使?内存、Cache和Cache一致性

https://blog.csdn.net/ZoeyyeoZ/article/details/51804647

MESI&MOESI协议

https://www.cs.cornell.edu/projects/ladis2009/talks/dean-keynote-ladis2009.pdf

参考:

https://zhuanlan.zhihu.com/p/296808047

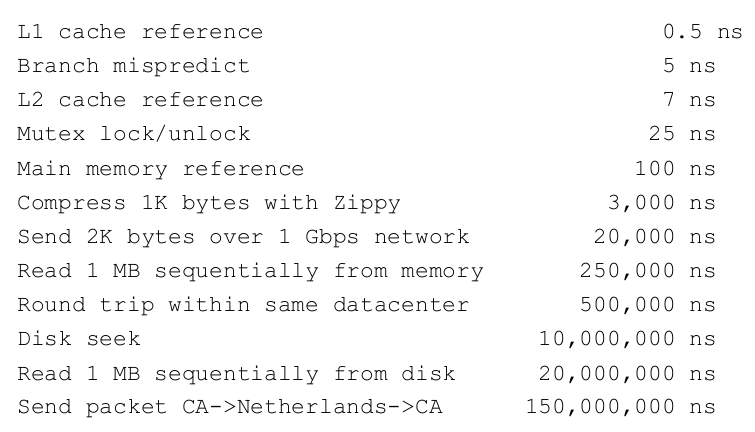

每个程序员都应该知道的延迟数字

L1 Cache分为ICache(指令缓存)和DCache(数据缓存)。

TLB:Translation Lookaside Buffer是一种缓存机制,存储了最近使用过的地址转换信息,以减少访问内存时的延迟。

https://zhuanlan.zhihu.com/p/31875174

细说Cache-L1/L2/L3/TLB

https://mp.weixin.qq.com/s/cSu-P-aDSXH0CYLN2HNrxw

深入理解Cache(上)

https://mp.weixin.qq.com/s/rml_wqePIx8vOk2ZO9_GMA

深入理解Cache(下)

https://mp.weixin.qq.com/s/Lydg1TMlNO_98Z-NF5BIBQ

理解CPU Cache

https://mp.weixin.qq.com/s/8g33nTI_-i9Rzmu-5Up-HA

高性能编程:三级缓存(LLC)访问优化

https://mp.weixin.qq.com/s/QidAD9OuVdEXFqxRMPx5lQ

响应速度不给力?解锁正确缓存姿势

https://mp.weixin.qq.com/s/ziJ8OFiLA1it3sQvycN7Mg

翻越缓存的三座大山

https://mp.weixin.qq.com/s/AekR-mv9EOD-4V5SKqI9YQ

一文看懂缓存

https://mp.weixin.qq.com/s/FY8sEX4acEUpCu_6ntArYw

CPU缓存L1/L2/L3工作原理

https://mp.weixin.qq.com/s/G4SpTC8DZ-l5kWBRGwSwGQ

Linux内存、Swap、Cache、Buffer详细解析

https://zhuanlan.zhihu.com/p/608663298

一篇论文讲透Cache优化

Cache Line

高速缓存其实就是一组称之为缓存行(cache line)的固定大小的数据块,其大小是以突发读或者突发写周期的大小为基础的。

每个高速缓存行完全是在一个突发读操作周期中进行填充或者下载的。即使处理器只存取一个字节的存储器,高速缓存控制器也启动整个存取器访问周期并请求整个数据块。缓存行第一个字节的地址总是突发周期尺寸的倍数。缓存行的起始位置总是与突发周期的开头保持一致。

https://zhuanlan.zhihu.com/p/37749443

计算机缓存Cache以及Cache Line详解

Bélády’s Algorithm

Bélády认为最好的缓存算法是:丢弃那些在将来最长时间不被使用的数据。显然这是一个理想化的算法,因为我们没有办法预测未来。但它可以作为衡量缓存算法优越度的一个理论上限。

László Bélády,1928年生,匈牙利计算机科学家。Technical University of Budapest本硕。IBM研究员。

LFU: least frequently used

LRU: least recently used

https://mp.weixin.qq.com/s/AdmEd1FHxpZUwSGYy3qggg

利用cpu缓存实现高性能程序

https://zhuanlan.zhihu.com/p/591436083

经典论文解读——Cache替换算法

Scratchpad Memory

除了Cache之外,Scratchpad memory(SPRAM)也是一种常见的内存缓冲硬件。

两者的区别是:

-

Cache通过硬件来管理每个位置上存放的数据;SPM没有硬件管理的替换策略,由程序员来管理数据的存放位置。因此,spm的控制逻辑比较简单,能耗也比较低。

-

当访存行为不规则时,cache中的硬件管理机制可以有效的管理数据。但当程序中的访存行为可以很容易的描述出来时,程序员可以根据程序的访存行为设计spm的数据存取方式,从而提高访存效率。

https://blog.csdn.net/weixin_48304306/article/details/125799814

Cache与Scratch-pad-memory(spm)的区别

Jim Keller

| Jim Keller: Work Experience | ||||

| Company | Title | Important Product |

||

| 1980s | 1998 | DEC | Architect | Alpha |

| 1998 | 1999 | AMD | Lead Architect | K7, K8v1 HyperTransport |

| 1999 | 2000 | SiByte | Chief Architect | MIPS Networking |

| 2000 | 2004 | Broadcom | Chief Architect | MIPS Networking |

| 2004 | 2008 | P.A. Semi | VP Engineering | Low Power Mobile |

| 2008 | 2012 | Apple | VP Engineering | A4 / A5 Mobile |

| 8/2012 | 9/2015 | AMD | Corp VP and Chief Cores Architect |

Skybridge / K12 (+ Zen) |

| 1/2016 | 4/2018 | Tesla | VP Autopilot Hardware Engineering |

Fully Self-Driving (FSD) Chip |

| 4/2018 | 6/2020 | Intel | Senior VP Silicon Engineering |

? |

| 2021 | Tenstorrent | President and CTO | TBD | |

C Model

在芯片的架构设计阶段需要对芯片进行建模(modeling),建模的主要目的是在大规模投入人力之前先用低成本的计算机软件实现目标芯片的主要功能,评估芯片的工作效果,验证设计思想,并作为后续开发活动的标准和依据。由于这里的软件开发一般使用C语言,所以也叫做C Model。

一般而言,C Model的功能定位可能会有以下几种:

-

作为算法模型的C版本,定义模块输入输出行为的标准,实现数据的bit-match;

-

在1的基础上,定义模块的内部结构和资源约束;

-

在2的基础上,精确定义模块的输入输出时序,实现cycle-accurate;

https://zhuanlan.zhihu.com/p/263012865

ASIC Design and C Model

IPC

IPC就是每个时钟周期(1Hz)执行指令的数量,但对于现代CPU,IPC这个参数已经不适用。因此现在是把使用测试程序得到的CPU单核成绩换算到1GHz,把每GHz的成绩称为IPC或PPC。奔腾4的频率与现代CPU差不多,但因PPC/IPC不到Intel 11代酷睿的1/5,所以在频率相同的时候,奔腾4的单核性能就不到11代酷睿的1/5。

CPU的IPC比频率更加重要,因为IPC代表了CPU核心的设计水平,频率则只要使用更新的工艺,就几乎一定能得到提升。

CPU的核心设计会影响提高频率的难度,通常IPC越高,频率就越难提高,但也不是决定性的因素。因为Intel的CPU不但IPC比国产CPU都高,频率还能超过5.0GHz。

龙芯认为在CPU核心逻辑设计水平接近同期的主流产品之前,没有必要过于注重工艺和频率。因此龙芯在中科院计算所时,每一代设计都在大幅度修改CPU核心的逻辑设计。

内存一致性

具有共享内存的系统中,所有的处理器都能访问到同一地址空间(比如:能看到同一个全局变量)。在这样的系统中,多个线程如何去更新全局变量,底层硬件和编程者要达成共识,并遵守相关的访问协议。这些协议被称为“内存一致性模型”。

x86使用的TSO和ARM的Relaxed模型相比,通过更复杂的硬件设计保证了更强的一致性,对软件的要求更松;ARM因为Relaxed模型比较宽松(几乎成了个分布式系统),原本x86靠硬件保证的东西就需要软件通过额外插入barrier来保证。

插barrier不管怎么样都是多了指令,对icache/uop cache有压力,访存后端也一般假设barrier出现得比正常访存少得多因此不会花大力气优化。

https://www.zhihu.com/question/350284825

既然x86的cpu是把cisc翻译成RISC再执行的,为什么arm模拟x86那么困难,性能差那么多呢?

https://zhuanlan.zhihu.com/p/422848235

内存一致性(Memory Consistency)

https://www.cl.cam.ac.uk/~pes20/weakmemory/

Relaxed-Memory Concurrency

机柜

机柜、板卡的尺寸规格也有工业标准,以方便不同厂商产品的互联和替换。

OCP(Open Compute Project)组织负责定义数据中心相关的工业标准。

官网:

https://www.opencompute.org

OAM:OCP Accelerator Module

UBB:Universal Base Board

https://zhuanlan.zhihu.com/p/339628067

开放计算的源起,对比标准x86服务器开放计算有哪些特点和创新?

https://zhuanlan.zhihu.com/p/571417872

开放整机柜服务器简史

RISC-V

https://mp.weixin.qq.com/s/LreWWlXAQL-dqQBCk93soQ

解读两大精简指令集:RISC-V和MIPS

https://mp.weixin.qq.com/s/5uie8Ci5dK_wy54Z70Gklg

RISC-V精简到何种程度?能省的都省了!

https://mp.weixin.qq.com/s/JNCC3C3Sq0Hzk_5VBcivng

RISC-V有何特别之处?

尽管Verilog曾经极大地推动了工程师设计能力的以指数级提升,但是在当下,随着芯片规模尤其是AI芯片规模的急剧增大,Verilog低效的描述方式已经被广为诟病。U.C. Berkeley在设计RISC-V的时候引入Chisel语言。

https://zhuanlan.zhihu.com/p/98097268

初学Chisel语言,看这篇就够了:最方便简洁的入门资料整理

您的打赏,是对我的鼓励